作者: Kaijie Zheng, Ning Zhang

### 摘要

BMS系统的工作电压普遍大于人体所能承受的安全电压,若绝缘性能下降将导致漏电流增大,对人身安全造成威胁。本文中介绍的绝缘监测电路使用NSI7258通过电池正母线对地、负母线对地绝缘电阻的计算和监测来判断绝缘性能,实现高精度和高可靠性的绝缘监测。

### 目录

| 1. 方案原理                  | 2 |

|--------------------------|---|

| 1.1.绝缘监测实现原理             | 2 |

| 2. 器件选型                  | 3 |

| 2.1.电阻选型                 | 3 |

| 2.1.1.电阻选型考量             | 3 |

| 2.1.2.400V/800V系统推荐电阻值   | 4 |

| 2.2.继电器选型                | 4 |

| 2.2.1.继电器漏电流对监测精度影响      | 4 |

| 2.2.2.继电器可靠性对系统可靠性的影响    | 5 |

| 3. 绝缘监测应用中的EMS注意项及推荐解决方案 | 6 |

| 3.1.绝缘监测应用潜在EMS问题        | 6 |

| 3.2.推荐应用电路分析             | 7 |

| 3.3.推荐PCB布局 ······       | 8 |

| 4. 修订历史                  | 9 |

### 1.方案原理

#### 1.1.绝缘监测实现原理

根据GB 18384《电动汽车安全要求》要求,在最大工作电压下,绝缘电阻需要大于500  $\Omega/V$ 。因此对于母线电压为VBUS的系统,绝缘电阻均需要满足大于以保障人身安全。当绝缘电阻劣化,绝缘监测电路应快速识别并发出报警。

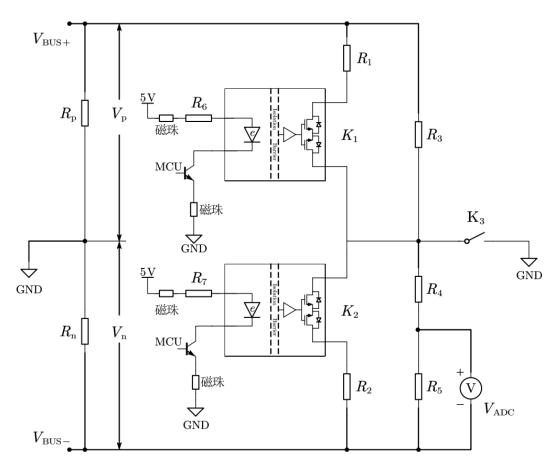

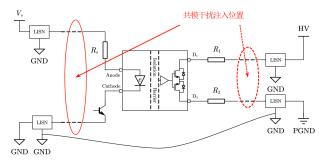

图1.1 绝缘监测电路推荐应用电路

绝缘监测电路推荐应用电路如图1.1所示,K1及K2为纳芯微固态继电器(Solid-State Relay, SSR) 产品在绝缘监测电路中的主要应用位置,芯片采用低压侧控制,即芯片低压侧参考地为车身地。该应用电路每隔2-3s通过K1、K2开关来进行一次绝缘监测电路Rp、Rn的阻值测量,通过开关K3实现绝缘监测电路是否工作的控制。绝缘监测过程中,K3处于常闭状态。

定义母线电压为VBUS,直流正母线到车身地的电压为Vp,车身地到直流负母线的电压为Vn。

当K1 断开, K2断开, 此时R5上电压为V0,则Vn0 = V0\*(R4+R5)/R5, Vp0 = Vbus - Vn0,可得计算公式(1):

$$\frac{V_{p0}}{V_{n0}} = \frac{R_p / / R_3}{R_n / / (R_4 + R_5)} \tag{1}$$

当K1 闭合, K2断开,此时R5上电压为V1,则Vn1 = V1\*(R4+R5)/R5, Vp1 = Vbus - Vn1,可得计算公式(2):

$$\frac{V_{p1}}{V_{n1}} = \frac{R_p / / R_3 / / R_1}{R_n / / (R_4 + R_5)}$$

(2)

由计算公式(1)和计算公式(2)可得:

$$R_n//(R_4 + R_5) = (\frac{V_{n1}}{V_{p1}} - \frac{V_{n0}}{V_{p0}}) \times R_1$$

(3)

当K1 断开, K2闭合,此时R5上电压为V2,则Vn2 = V2\*(R4+R5)/R5, Vp2 = Vbus - Vn2,可得计算公式(4):

$$\frac{V_{p2}}{V_{n2}} = \frac{R_p//R_3}{R_n//(R_4 + R_5)//R_2}$$

(4)

由计算公式(1)和计算公式(4)可得:

$$R_{\rm p}//R_3 = (\frac{V_{\rm p2}}{V_{\rm n2}} - \frac{V_{\rm p0}}{V_{\rm n0}}) \times R_2 \tag{5}$$

公式(3)和公式(5)是绝缘电阻计算的结果。

### 2.器件选型

#### 2.1.电阻选型

#### 2.1.1. 电阻选型考量

通常,电路设计上,令 $R_1=R_2$ < $R_3=R_4$ ,并存在如下设计考量:

对ADC输入电压的考量: R5上的电压需要一直小于ADC的最大输入电压,最大值接近ADC的最大输入电压,以保证ADC的输出精度。所以R5/(R4+R5)\*VBUS需要接近ADC的最大输入电压,以此得到R5、R4的比例。

对ADC内阻的考量: R5作为ADC采样的输入口,其阻值需要小于ADC的内阻(如<RADC/10),以便忽略ADC内阻影响。

对绝缘阻抗影响的考量: K1和K2开关过程中,监测电路中的R1和R2分别并联在Rp和Rn上,如果R1、R2过小,将导致实际上的绝缘电阻Rp//R1和Rn//R2大幅降低。

对识别精度的考量:结合公式(4),当Rp//R3劣化达到小于临界值500· $V_{BUS}$ 后,当( $\frac{V_{p2}}{V_{n2}} - \frac{V_{p0}}{V_{n0}}$ )  $xR_2$  <500· $V_{BUS}$ 时MCU识别到绝缘电阻劣化并报警。因此需要R2小一些以便Vp2和Vn2在数值上有足够的差异来抵消ADC精度误差。

对Settle time的考量:在实际系统中,部分客户车身地和电池地中间并联Y电容(即与Rn并联),存在RC充放电过程,R1、R2需要小一些以便于减少settle time。如R1、R2取得过小,将导致 K12闭合时的并联等效阻抗 $R_{\rm n}//R_{\rm 3}//R_{\rm 1}$ 、 $R_{\rm n}//(R_{\rm 4}+R_{\rm 5})//R_{\rm 2}$ 偏小,也对人身安全造成威胁。

#### 2.1.2. 400V/800V系统推荐电阻值

基于上述分析,可以基于下表设计绝缘监测电路分压电阻。

| R <sub>1</sub> , R <sub>2</sub> | 500 kΩ |

|---------------------------------|--------|

| R <sub>3</sub> 、R <sub>4</sub>  | 3 ΜΩ   |

| R <sub>5</sub>                  | 12 kΩ  |

表2.1 400V系统推荐电阻选型

| $R_1$ , $R_2$  | 1 ΜΩ  |

|----------------|-------|

| $R_3$ , $R_4$  | 6 ΜΩ  |

| R <sub>5</sub> | 12 kΩ |

表2.2 800V系统推荐电阻选型

### 2.2.继电器选型

#### 2.2.1. 继电器漏电流对监测精度影响

绝缘电阻劣化到小于500· $V_{BUS}$ 时系统监测到此现象应报警。以VBUS = 800V的系统为例,按标准要求绝缘电阻应大于400kΩ,若K1、K2上漏电流小于1  $\mu$ A,其等效阻抗大于800MΩ,远大于绝缘电阻Rp、Rn,对于400kΩ测量带来的误差小于0.05%。若K1、K2上漏电流为10  $\mu$ A,其等效阻抗等于400 MΩ,测量误差约为0.5%。

因此,漏电流越大 ,对于测量精度的影响越大。选用漏电流小(<1 μA)的纳芯微SSR产品来实现 K1、K2的开通、关断功能将有益于提升测量精度,避免误报警。

#### 2.2.2. 继电器可靠性对系统可靠性的影响

传统机械继电器开关寿命受限,一旦到达最大开关次数,系统绝缘监测功能失效,人身安全隐患突 出。因此机械继电器已经基本退出此应用场景。

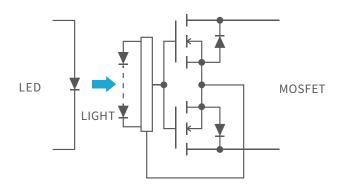

传统PhotoMOS目前使用较多。PhotoMOS在控制侧发光二极管(LED)通电流后,光敏二极管接收到光的照射,由光电效应产生电流从而控制高压侧MOS导通。

图3.1 PhotoMOS原理

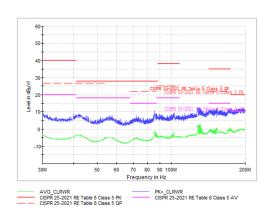

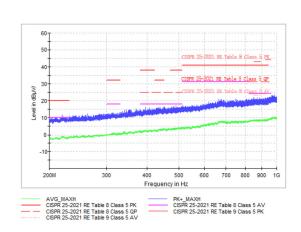

LED经过长时间使用后,发光强度将会降低。主流光耦供应商对于PhotoMOS产品使用寿命进行了预测,1000小时后阈值电流就会升高10%,11年后阈值电流需要提高5倍以上。若按照数据手册中的阈值电流进行设计,光敏二极管接收到的能量不足,将导致误码失效。改善的方法只能是设计较大的输入电流来解决光衰问题。但是另一方面,更大电流带来更高的温度,高温将导致发光二极管将电信号转化为光信号和光敏二极管将光信号转化为电信号的效率降低,同时,由于高温寿命问题,PhotoMOS一般限制在最大85°C环境温度下。多种因素使得光耦产品可靠性受到极大的挑战。采用容隔或者磁隔的固态继电器来替代类似光耦的PhotoMOS,可以极大提高系统的可靠性。纳芯微电子公司开发的NSI7258产品是一款通过EMI CISPR25 CLASS5标准,同时采用高可靠性隔离技术的产品,将强大的技术创新能力与车规高可靠性的质量管理体系结合,为绝缘监测系统提供高性能,高可靠性的解决方案。

图3.2 NSI7258 EMI测试结果

### 3.绝缘监测应用中的EMS注意项及推荐解决方案

#### 3.1.绝缘监测应用潜在EMS问题

在新能源汽车中,电子组件的可靠性对车辆的整车性能起着至关重要的作用。特别是,在面对恶 劣电磁干扰环境下,确保车辆集成的各单元能够正常运作,符合电磁兼容性标准,成为了一个关 键问题。

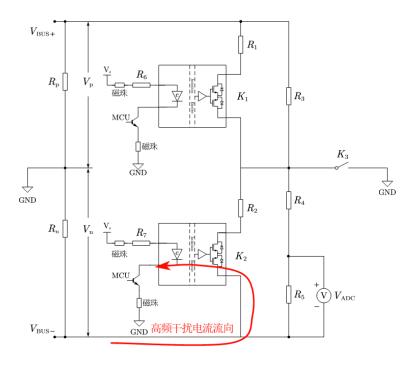

诸如辐射抗扰(RI)、大电流注入(BCI)、手持发射机抗扰(PTI)等部分EMS测试,可等效为在芯片的高、低压侧两端加一高频电流源,如图4.1所示。尽管电路板上及空间中存在寄生电容高频电流泄放路径,但仍然会有部分电流直接注入芯片内部。在电流频率较高时(约几百MHz),隔离电容呈现阻抗相对较低,成为潜在电流通路,且当电路上无其他高频电流泄放路径设计时,电流将穿过隔离电容,经由芯片高压侧回流至低压侧,形成电流环路,将可能干扰芯片正常工作。

图4.1 部分EMS测试等效模型

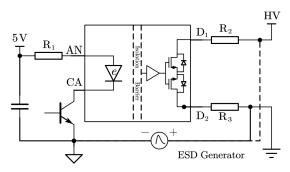

BMS系统产品在设计验证环节中,需要对进行系统ESD测试,其中下电模式,用以模拟产品在制造、组装、测试、存放及搬运等过程中,因人为接触所导致人体积累的静电的泄放过程,评估产品抵抗静电放电破坏能力。在该测试中,需要将ESD枪的地接至设备机壳地,放电点为暴露在表面的零部件(机壳、螺丝等)及人能直接接触到的接插件的每个Pin脚,且通常需要通过±8kV测试需求。由于固态继电器产品跨接在BMS系统高压域与低压域间,若芯片位置设计不合理,±8kV的ESD电压将直接施加在芯片隔离带两侧,且无其他ESD电流泄放路径。测试等效模型如图4.2所示。

图4.2 系统ESD测试等效模型

为避免上述电磁兼容问题影响或损坏芯片,可根据如下推荐原理图及布局设计电路。

#### 3.2.推荐应用电路分析

如图2.1,在绝缘监测应用电路中,推荐将SSR放至电桥中点两侧,经过大分压电阻R1、R2后再与高压母线 $V_{BUS+}$ 及 $V_{BUS-}$ 连接。以K1为例,由于K1的D1、D2引脚至高压母线 $HV_{+}$ 及 $HV_{+}$ 线路上均存在大分压电阻,使得高频干扰电流难以灌入SSR芯片,同时K3导通,进一步提供了高频干扰电流泄放路径。当系统注入干扰时,干扰电流流通路径为 $V_{BUS+}$   $\rightarrow$   $R_{1}$   $\rightarrow$   $K_{1}$  导通电阻 $R_{dson}$   $\rightarrow$   $K_{3}$  与通电阻 $R_{dson}$   $\rightarrow$   $R_{3}$   $\rightarrow$   $R_{4}$   $\rightarrow$   $R_{3}$   $\rightarrow$   $R_{4}$   $\rightarrow$   $R_{4}$   $\rightarrow$   $R_{3}$   $\rightarrow$   $R_{4}$   $\rightarrow$   $R_{5}$   $\rightarrow$

电路的欠佳设计如图4.2所示,与图2.1不同,K2与R2位置互换,直接与相连,使得K1与K2表现出不同的EMS及ESD性能。由于缺少了分压大电阻的阻挡,高频电流将直接通过D2引脚直接注入K2,同时,由于K2的D1引脚与电桥中点间存在大分压电阻R2,隔离电容的阻抗相对更小,干扰电流无法经由K3流至车身地GND,而是直接经过K2的隔离电容回到车身地。干扰电流流通路径为HV $\rightarrow$ K2隔离电容C $_{ISO}\rightarrow$ 车身地GND。由于电流流经SSR隔离电容,SSR存在受干扰误工作风险。同时,在系统ESD测试中,ESD电压将由K2的隔离电容直接承压,当施加的ESD电压过高,将导致芯片损坏。

图4.3 绝缘监测欠佳设计

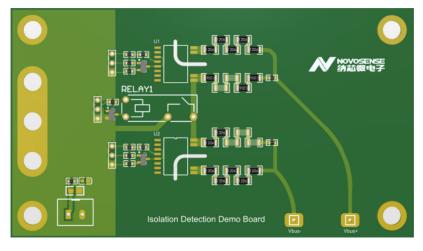

#### 3.3.推荐PCB布局

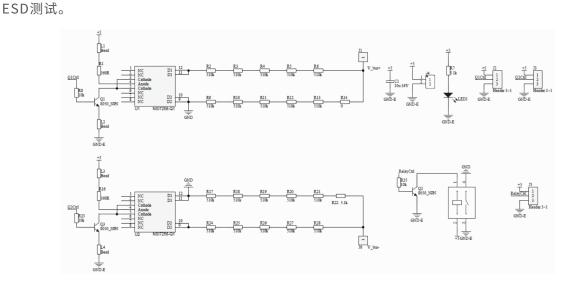

PCB板布局 PCB 布局对EMS性能非常重要。根据4.1节中的电路优化设计思路,给出如下PCB电路设计参考设计。请参阅图 4.4 推荐原理图、图4.5 推荐布局和下面的 PCB 布局指南:

- 1.为符合隔离和安全要求,一次侧和二次侧必须物理隔离。爬电距离和间隙必须符合适用于该应用的安全标准。考虑到一般PCB电路板为CTIⅢ级,需进行开槽以保证足够的爬电。

- 2.为保证足够的抗共模干扰性能,应充分注意PCB板上走线,考虑分布寄生电容的影响,避免因同层、跨层走线过近,产生寄生低阻抗路径,使干扰电流在芯片高压侧直接注入芯片D1、D2引脚。同时,在磁珠附近,应避免大面积铺地,避免电流通过空间电容绕过磁珠,降低磁珠效果。 经实验验证,该推荐电路可通过100k-400MHz ISO11452-4 Level 4的BCI测试及±10kV的系统

图4.4 绝缘监测推荐原理图

图4.5 绝缘监测推荐布局

### 4.修订历史

| 版本  | 描述     | 作者                      | 日期        |

|-----|--------|-------------------------|-----------|

| 1.0 | 创建应用笔记 | Kaijie Zheng,Ning Zhang | 2025/4/10 |

|     |        |                         |           |

|     |        |                         |           |

销售联系方式: sales@novosns.com; 获取更多信息: www.novosns.com

### 重要声明

本文件中提供的信息不作为任何明示或暗示的担保或授权,包括但不限于对信息准确性、完整性,产品适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的陈述或保证。

客户应对其使用纳芯微的产品和应用自行负责,并确保应用的安全性。客户认可并同意:尽管任何应用的相关信息或支持仍可能由纳芯微提供,但将在产品及其产品应用中遵守纳芯微产品相关的所有法律、法规和相关要求。

本文件中提供的资源仅供经过技术培训的开发人员使用。纳芯微保留对所提供的产品和服务进行更正、修改、增强、改进或其他更改的权利。纳芯微仅授权客户将此资源用于开发所设计的整合了纳芯微产品的相关应用,不视为纳芯微以明示或暗示的方式授予任何知识产权许可。严禁为任何其他用途使用此资源,或对此资源进行未经授权的复制或展示。如因使用此资源而产生任何索赔、损害、成本、损失和债务等,纳芯微对此不承担任何责任。

有关应用、产品、技术的进一步信息,请与纳芯微电子联系( www.novosns.com )。

苏州纳芯微电子股份有限公司版权所有