AN-15-0016

作者: Huojun Long

# 摘要

纳芯微专门为E-mode GaN HEMT推出了单通道的驱动芯片NSD2012N。该芯片集成专门的电压调节器,可分别输出5V~6.5V可调驱动正压和-0.5V~-2.5V的可调关断负压,抽灌峰值电流为2A/-4A,可以满足绝大部分GaN HEMT的应用需求。另外芯片还提供了一个5V的直流输出电压,其最大输出电流能力为50mA,可以满足数字隔离器等器件的供电需求。本篇应用笔记主要针对于该芯片的外围器件选型和应用进行介绍。

### 目录

| 1. 典型应用电路                                            | 2 |

|------------------------------------------------------|---|

| 1.1. VCC上电时的工作时序                                     | 2 |

| 1.2. VDDL电压设置和参数选取                                   | 3 |

| 1.3. 5V LDO的应用                                       | 4 |

| 1.4. VEE电压设置和参数选取                                    | 4 |

| 1.5. 半桥中的高边上电时序和器件选取                                 | 5 |

| 2. 驱动电阻的选取和功耗计算 6                                    | 6 |

| 3. PCB Layout建议 ···································· | 8 |

| 4. 修订历史                                              | 9 |

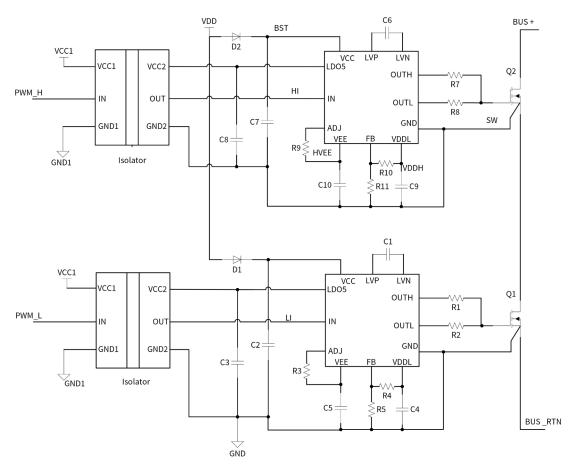

### 1.典型应用电路

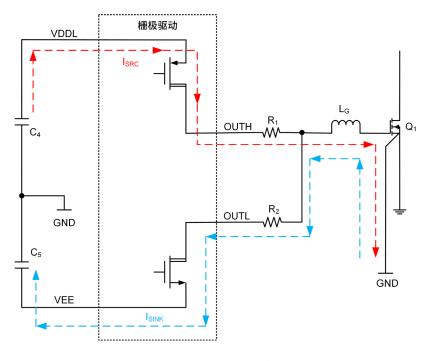

图1.1 NSD2012N 典型应用电路

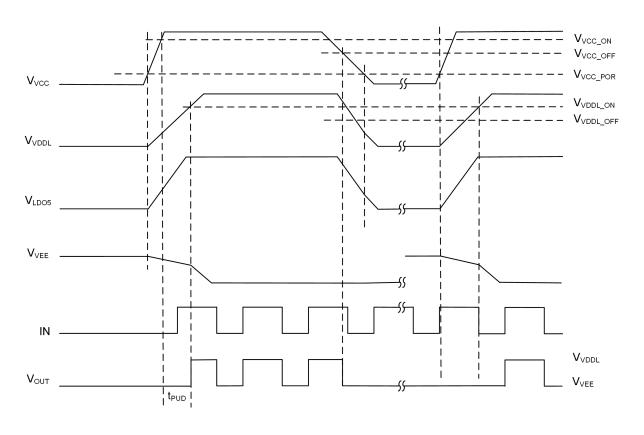

#### 1.1.VCC上电时的工作时序

NSD2012N的具有欠压锁死功能。当VCC相对GND的电压上升到POR电压后,LDO5、VDDL和LVEE的电压开始建立。在VDDL电压没有到达欠压点之前,VEE会采用约3mA的电流进行负向充电;当VDDL的电压超过欠压点之后,VEE的负压会快速建立。VCC和GND之间要就近放置ESL和ESR小的电容,电容建议不小于1uF。当VCC掉电到欠压点后,输出被拉低,VEE电压开始慢慢上升到0V。图2是VCC的上下电时序图。需要注意的是VCC上电过程中会有约200mA的冲击电流,持续时间几十微秒。

图1.2 VCC的上电时序

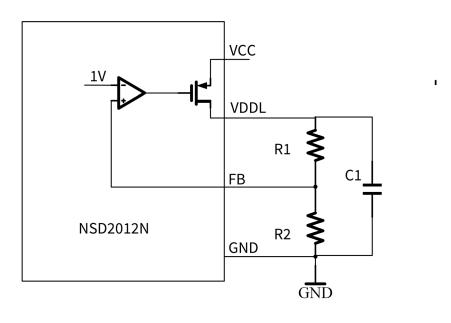

#### 1.2.VDDL电压设置和参数选取

VDDL是驱动电压LDO的输出脚,给功率GaN HEMT提供驱动电流和电压。VDDL的输出电压通过公式(1)的配置参数来设定。为了保证VDDL的可靠稳定输出,需要在VDDL和GND之间并联一个不小于470nF的电容,其输出电压需要小于VCC电压。其中电阻R2的推荐范围为 $1k\Omega\sim20k\Omega$ ,电容C1的推荐范围为470nF $\sim1uF$ ,其ESR和ESL要尽可能小。需要注意的是,VDDL的推荐输出电压范围为5V $\sim6.5V$ ,超过6.5V的输出电压可能会导致芯片失效;另外,并联的电容越大,芯片的开机时间越长。

图1.3 VDDL电压设计

$$V_{VDDL} = \frac{R_1 + R_2}{R_2} \times 1V \tag{1}$$

#### 1.3.5V LDO的应用

LDO5是5V的LDO输出。为了保证LDO5的可靠稳定输出,需要在LDO5和GND之间并联一个100nF~1uF的电容。即使LDO5不使用,也需要并联该电容。LDO5的最大输出电流能力为50mA,可以为其他器件或电路提供必要的供电。当LDO5的负载电流过大时,芯片可能出现过温或过流保护,导致无驱动输出。

#### 1.4.VEE电压设置和参数选取

VEE是负压LDO的输出,输出电压范围为-0.5V~-2.5V。当ADJ悬空时,VEE默认输出-2.5V;当需要调整VEE的输出电压时,需要在VEE和ADJ之间并联一个电阻,电阻值与VEE的电压关系见下表。

| 表1.电阻与 | VEE之间的关系 |

|--------|----------|

|        |          |

| Radj     | 单位 | 负压(VEE) | 单位 |

|----------|----|---------|----|

| 47       | ΚΩ | -0.5    | V  |

| 110      | ΚΩ | -1.0    | V  |

| 232      | ΚΩ | -1.5    | V  |

| Floating | ΚΩ | -2.5    | V  |

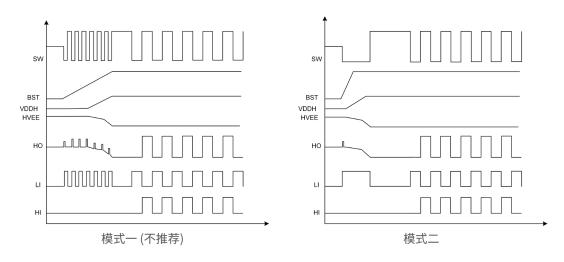

#### 1.5. 半桥中的高边上电时序和器件选取

对于图1.1的半桥电路,高边BST网络建议采用图1.4中模式二的时序进行上电。如果采用图1.4模式一的时序进行上电,在低边LI输入窄脉冲期间,HVEE和VDDH没有建立完全,高边的 GaN HEMT栅极会因为米勒电容出现误脉冲,可能导致上下管直通失效。采用模式二的时序进行上电。低边输入LI的首个脉冲足够宽,BST、VDDH和HVEE成功建立,高边GaN HEMT的栅极被拉到HVEE,确保上下管不会直通。

备注:对于高边采用隔离供电的半桥应用,主功率电路工作前,BST电压已建立,上电时序没有限制。

图1.4NSD2012N BST的自举上电时序

对于图1.1中半桥电路,当高边NSD2012N的供电电压低于其VCC的欠压点时,高边输出会被拉低。为了确保高边驱动正常工作,高边NSD2012N的VCC对其GND应并联一颗电容,如果工作中存在待机模式,可以采用公式(2)进行电容选取。

$$C_{BST} \ge \frac{(I_{BST_Q} + I_{VDDH}) \times t}{(V_{CC} - V_{Diode} - V_{BST\_min})}$$

(2)

IBST\_Q: NSD2012N的最大静态电流

IVDDH: 图1.1中 高边VDDH网络的采样支路的分流

Vcc: VCC的供电电压

VDiode: 图1.1中Bootstrap的二极管D2压降

VBST\_min: VCC的最小工作电压

CBST: 图1.1中高边BST网络的供电电容C7

t: 高边待机时间

高边的VCC对其GND的并联电容建议不小于1uF,且ESR和ESL要小,就近放置。

为了减小自举二极管功耗和反向恢复对高边NSD2012N供电电压的影响,在保证耐压满足要求的情况下,建议选用快恢复二极管或氮化硅肖特基二极管。另外,开机瞬间高边供电电容的瞬态充电电流会比较大,系统应用时需要注意,可以串联一个 $10^{-10}\Omega$ 的限流电阻。

# 2.驱动电阻的选取和功耗计算

GaN HEMT的速度快,di/dt和dv/dt高。为了更好的控制GaN HEMT的开关速度,NSD2012N的抽灌电流引脚是采用分开设计,如图2.1所示。GaN HEMT开通时,受漏极高的dv/dt和米勒电容Coo的影响,栅极电压可能出现振荡或过冲,其电流路径如图2.1中的Isrc所示。这种振荡或过冲将引起GaN HEMT功耗增加或失效。为了避免过大的振荡或过冲,开通时总的栅极等效电阻建议不小于公式(3)中给出的值。

图2.1GaN HEMT 驱动电路

$$R_{G(eq)} \ge 2 \times \sqrt{\frac{L_G}{C_{GS}}}$$

(3)

其中Lg为开通时总的等效寄生电感; Rg(eg)为开通时总的等效驱动电阻; Cgs为GaN HEMT的栅极等效电容。

GaN HEMT关断时,受驱动回路寄生电感和栅极关断速度的影响,栅极电压可能出现负向过冲或振荡,过大的负向过冲或振荡可能导致栅极击穿或误导通。其电流路径如图2.1中的 $I_{SINK}$ 所示。设计时要避免过大的负向过冲或误开通发生,建议关断电阻不小于 $1\Omega$ 。

从图2.1可以看到,开通和关断时的电流路径Isrc和Isink有所不同,对应的开通和关断时总的等效寄生电感Le和等效电阻R<sub>G(eq)</sub>会有所差异。其中开通时总的等效寄生电感Le包含了的正电源VDDL部分的寄生电感,而关断时Le则包含负电源VEE部分的寄生电感,分析计算时要注意。

在图1.1的应用中驱动电阻的功耗和NSD2012N的总功耗可以通过公式(4)~(6)来计算

$$P_{R1} \approx 0.5 \times Q_G \times (V_{VDDL} + V_{VEE}) \times f_{SW} \times \frac{R_1}{R_{OH} + R_1}$$

(4)

$$P_{R2} \approx 0.5 \times Q_G \times (V_{VDDL} + V_{VEE}) \times f_{SW} \times \frac{R_2}{R_{OL} + R_2}$$

(5)

$$P_{IC} \approx V_{CC} \times (2 \times Q_G \times f_{SW} + I_{VCC_Q} + I_{LDOS} + \frac{1}{R_5}) - (P_{R1} + P_{R2})$$

(6)

PRI: 驱动开通电阻的功耗

PR2: 驱动关断电阻的功耗

Pic: NSD2012N的总功耗

Qg: GaN HEMT的栅极电荷

VDDL: VDDL的输出电压

fsw: 工作时的开关频率

R1: 驱动回路的开通电阻

R2: 驱动回路的关断电阻

RoH: NSD2012N的OUTH脚的上拉电阻,典型值为 $0.5\Omega$  RoL: NSD2012N的OUTL脚的下拉电阻,典型值为 $1.4\Omega$

Vcc: VCC的供电电压

Ivcc\_q: VCC的静态工作电流

ILDO5: LDO5的负载电流

R5: FB对GND的电阻

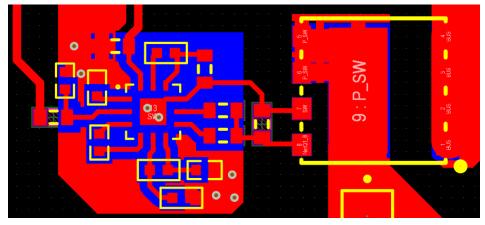

### 3.PCB Layout建议

为了减小噪声对芯片的干扰,PCB布局布线要注意以下几点:

- 驱动器尽可能靠近GaN HEMT,开通和关断的电流路径尽可能短,以便减小回路中的杂散电感带来的影响。

- VCC供电的电容尽可能靠近VCC和GND引脚,建议采用低ESR、低ESL的MLCC电容,且PCB走线尽可能在同一层。

- VDDL对GND之间放置一个不小于470nF的低ESR、低ESL电容,该电容尽可能靠近VDDL和GND。

- 驱动电阻尽可能靠近功率 GaN HEMT的栅极,且驱动走线宽度建议不小于0.5mm。

图3.1NSD2012N PCB Layout 示例

### 4.修订历史

| 版本  | 描述     | 作者          | 日期       |

|-----|--------|-------------|----------|

| 1.0 | 创建应用笔记 | Huojun Long | 2025/9/5 |

销售联系方式: sales@novosns.com; 获取更多信息: www.novosns.com

# 重要声明

本文件中提供的信息不作为任何明示或暗示的担保或授权,包括但不限于对信息准确性、完整性,产品适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的陈述或保证。

客户应对其使用纳芯微的产品和应用自行负责,并确保应用的安全性。客户认可并同意:尽管任何应用的相关信息或支持仍可能由纳芯微提供,但将在产品及其产品应用中遵守纳芯微产品相关的所有法律、法规和相关要求。

本文件中提供的资源仅供经过技术培训的开发人员使用。纳芯微保留对所提供的产品和服务进行更正、修改、增强、改进或其他更改的权利。纳芯微仅授权客户将此资源用于开发所设计的整合了纳芯微产品的相关应用,不视为纳芯微以明示或暗示的方式授予任何知识产权许可。严禁为任何其他用途使用此资源,或对此资源进行未经授权的复制或展示。如因使用此资源而产生任何索赔、损害、成本、损失和债务等,纳芯微对此不承担任何责任。

有关应用、产品、技术的进一步信息,请与纳芯微电子联系( www.novosns.com )。

苏州纳芯微电子股份有限公司版权所有