# 使用集成隔离电源的隔离运放NSI36xx 进行低EMI应用设计

AN-13-0017

作者：徐佳华，刘雅竹

# 使用集成隔离电源的隔离运放NSI36xx 进行低EMI应用设计

## 摘要

随着工业技术的进步，各类电子设备小型化的发展需求使电磁干扰（Electro Magnetic Interference, EMI）成为系统应用的一大难题。为了提高系统集成度，简化系统供电设计，纳芯微电子推出新一代集成隔离电源的隔离采样产品NSI36XX系列。NSI36XX系列在延续上一代隔离采样产品NSI13XX高精度、高可靠性的基础上，集成了隔离电源（包含内置片上变压器基板），并且提供电压采样、电流采样以及不同输入范围的料号选择，满足客户的不同应用场景需求。

辐射发射测试是EMI测试中重要的一部分，在工业控制、新能源汽车等不同领域，国际无线电干扰特别委员会（CISPR）规定了不同的测量标准。例如，工业控制应用一般参照CISPR 32测量，汽车应用一般参照CISPR 25进行测试评估。也有些车企对于辐射发射测试制定了企业标准来进行评估。

本文针对NSI36XX辐射发射来源，提供PCB布局建议和EMI改善方案，为客户低EMI应用设计提供参考。

## 目录

|                       |    |

|-----------------------|----|

| 1. 什么是EMI             | 2  |

| 2. NSI36XX产品介绍和辐射发射来源 | 2  |

| 2.1. NSI36XX产品介绍和选型表  | 2  |

| 2.2. NSI36XX辐射发射来源    | 3  |

| 3. PCB布局建议和案例         | 4  |

| 3.1. PCB布局建议          | 4  |

| 3.2. VDD、GND串联磁珠改善EMI | 6  |

| 3.3. 长输入信号线对EMI的影响    | 7  |

| 4. 多颗芯片应用中的辐射发射情况     | 8  |

| 5. 修订历史               | 10 |

# 使用集成隔离电源的隔离运放NSI36xx 进行低EMI应用设计

## 1.什么是EMI

EMC (Electromagnetic Compatibility) 即电磁兼容性，是指电子设备或系统在预期电磁环境中，既不产生超出允许范围的电磁干扰，又能承受外界电磁干扰而正常工作的能力，包含电磁干扰EMI (Electromagnetic Interference) 和电磁抗扰度EMS (Electromagnetic Susceptibility)。EMI是指在处于一定环境中的设备和系统正常运行时，不应产生超过相应标准所要求的电磁能量。EMS是指设备抵抗外界电磁干扰、维持正常功能的能力。本文主要讨论EMI中的辐射发射抑制方案。

辐射发射的产生和辐射骚扰源、传输路径密切相关。对于芯片来说，辐射骚扰源一般是内部工作时高频的时钟信号（快速变化的电平）或者高频变化的电流。传输路径一般指天线，导线长度（芯片内部或者PCB走线）较波长时，天线效应显著，辐射干扰会比较明显，而天线较短时辐射能得到有效的抑制和改善。所以除了一些空间屏蔽措施，合理的PCB布局也能在一定程度上有效改善系统辐射发射性能。

## 2.NSI36XX产品介绍和辐射发射来源

### 2.1.NSI36XX产品介绍和选型表

新一代集成隔离电源的隔离采样芯片NSI36xx系列是纳芯微NSI13xx系列的全面升级，包括隔离电流放大器NSI360x系列、隔离电压放大器NSI361x系列、内部集成比较器和单端比例输出的NSI36C00R/NSI36C1xR系列。

NSI36xx系列可广泛用于工业电机驱动、光伏逆变器、服务器电源、新能源汽车主驱、车载充电桩等高压系统的电流、电压采样，通过集成隔离电源、灵活的输出配置和内置保护功能，帮助工程师在系统设计中支持更高的功率密度，并简化外围电路。NSI36xx系列选型表如下。

# 使用集成隔离电源的隔离运放NSI36xx 进行低EMI应用设计

| 类型      | 料号               | 工规/车规 | 输入范围   | 增益   | 输出类型 | 是否带比较器 |

|---------|------------------|-------|--------|------|------|--------|

| 电压检测放大器 | NSI3611D-DSWR    | 工规    | 0~2V   | 1    | 差分输出 | N      |

|         | NSI3612D-DSWR    | 工规    | ±1V    | 2    | 差分输出 | N      |

|         | NSI36C11R-DSWR   | 工规    | 0~2V   | 比例增益 | 单端输出 | Y      |

|         | NSI36C12R-DSWR   | 工规    | ±1V    | 比例增益 | 单端输出 | Y      |

|         | NSI3611D-Q1SWR   | 车规    | 0~2V   | 1    | 差分输出 | N      |

|         | NSI3612D-Q1SWR   | 车规    | ±1V    | 2    | 差分输出 | N      |

|         | NSI36C11R-Q1SWR  | 车规    | 0~2V   | 比例增益 | 单端输出 | Y      |

|         | NSI36C12R-Q1DSWR | 车规    | ±1V    | 比例增益 | 单端输出 | Y      |

| 电流检测放大器 | NSI3600D-DSWR    | 工规    | ±250mV | 8.2  | 差分输出 | N      |

|         | NSI3602D-DSWR    | 工规    | ±50mV  | 41   | 差分输出 | N      |

|         | NSI36C00R-DSWR   | 工规    | ±250mV | 比例增益 | 单端输出 | Y      |

|         | NSI3600D-Q1SWR   | 车规    | ±250mV | 8.2  | 差分输出 | N      |

|         | NSI3602D-Q1SWR   | 车规    | ±50mV  | 41   | 差分输出 | N      |

|         | NSI36C00R-Q1SWR  | 车规    | ±250mV | 比例增益 | 单端输出 | Y      |

## 2.2.NSI36XX辐射发射来源

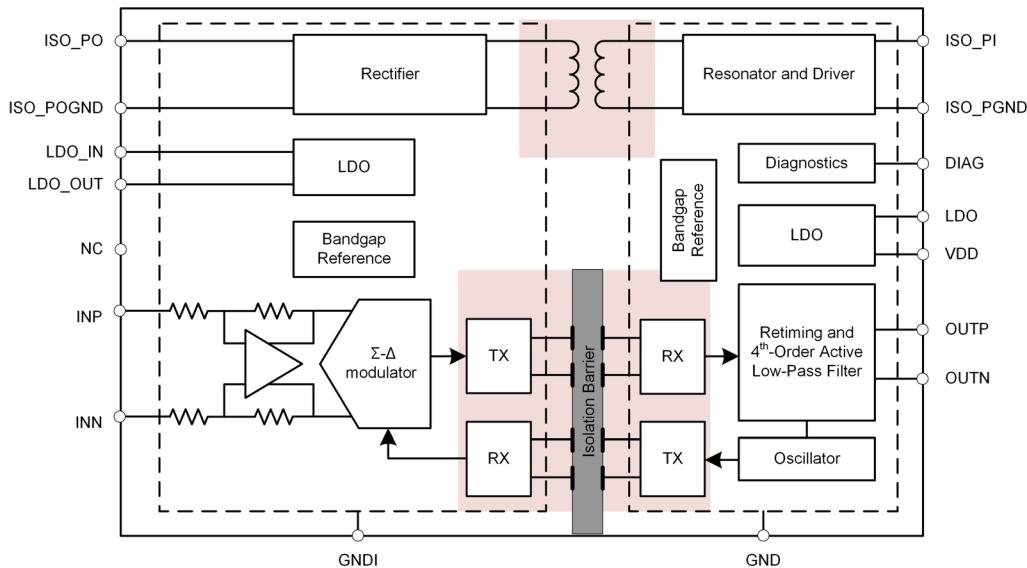

NSI36XX系列产品辐射发射骚扰源类似，以NSI3600D为例进行分析，图1.1为NSI3600D的功能框图。

NSI3600D主要有两个辐射发射骚扰源：信号链数据传输的电容隔离屏障和隔离电源变压器。

隔离屏障的电容通过高频充放电来传输数据，充放电过程中相反方向的正负电荷流过电容会相互抵消，但是如果电荷流之间存在差异无法完全抵消，就会在原副边地之间注入电磁能量，而隔离屏障中能量没有返回路径，就会形成偶极子天线向外辐射。

隔离电源变压器原副边之间存在寄生电容，原边驱动在原副边的地之间产生开关频率（31MHz）的共模电压波动，共模电压加在寄生电容两端产生的电流没有返回路径，就会形成偶极子天线，向外辐射能量。由于隔离电源传输的能量远大于电容隔离屏障传输的能量，隔离电源变压器是NSI3600D最主要的辐射发射来源。

# 使用集成隔离电源的隔离运放NSI36xx 进行低EMI应用设计

图 1.1 NSI3600D的功能框图

以上两个辐射发射骚扰源都是通过器件引脚以及引脚连接的导线、平面向外辐射，尽量缩短器件引脚的布线，可以有效限制辐射发射。

## 3.PCB布局建议和案例

### 3.1.PCB布局建议

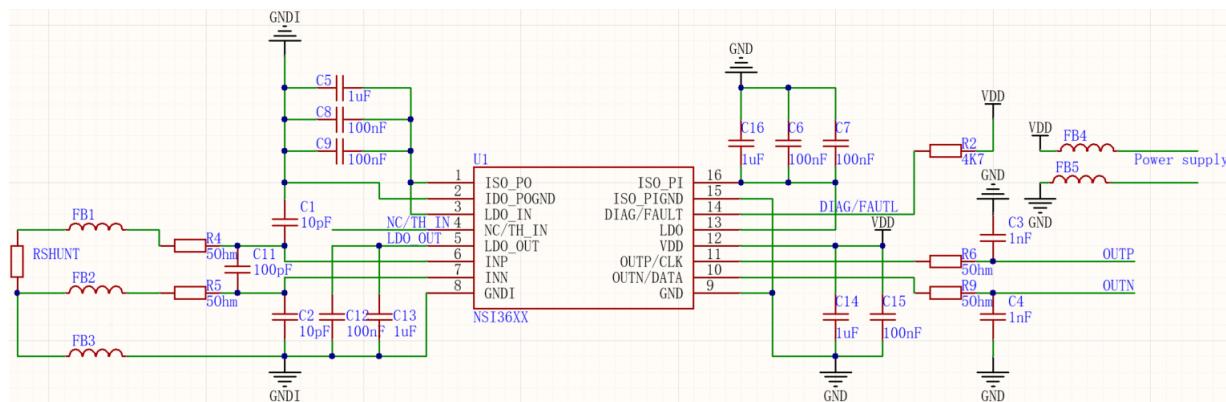

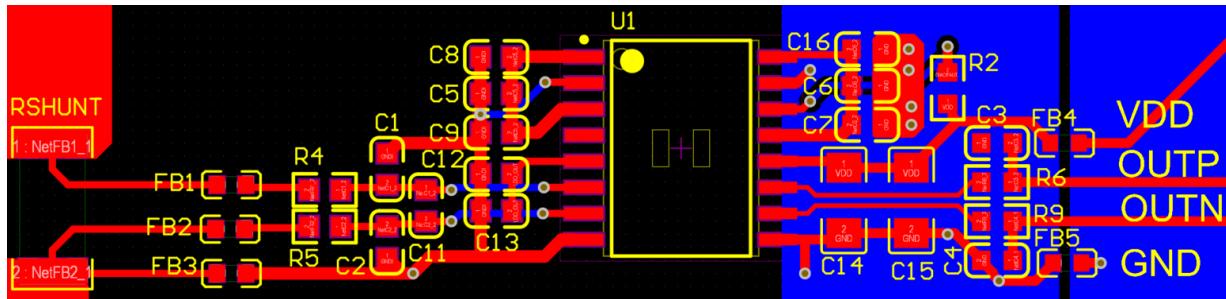

图2.1和图2.2分别给出了NSI36XX典型应用电路和PCB布局案例。以下是优化PCB布局性能的一些关键指南或注意事项：

- VDD、ISO\_PO、ISO\_PI 和 LDO\_OUT 引脚的滤波电容和旁路电容应分别尽可能靠近引脚放置，为高频噪声提供较短的接地返回路径。对于同一引脚的多个滤波电容，较小值的电容应放置得更靠近引脚，以便更好地滤除高频噪声。在噪声环境下，电源引脚 VDD 可额外使用一个 1~10 $\mu$ F 的电容。

- 元器件放置尽量减小信号线长度。将分流电阻放置在靠近 INP 和 INN 输入引脚的位置，并保持两条连接的布局对称，且尽量靠近 NSI3600D 的输入引脚。这样可以最小化连接的回路面积，减少杂散磁场干扰测量信号的可能性。

# 使用集成隔离电源的隔离运放NSI36xx 进行低EMI应用设计

- 芯片下方的空间应避免铺铜、走线、焊盘和过孔，以确保良好的绝缘性能。此外，芯片下方的走线可能会耦合隔离器的偶极子辐射能量，起到天线的作用，从而影响EMI性能。

- 适当的地平面铺铜可以减少环路面积，为信号提供最短的返回路径，如低压侧供电地平面。但在某些敏感节点，如高压侧隔离电源输出地，大面积铺地会形成天线，恶化EMI辐射发射。因此不要在高压区域设置接地平面，通过短线将高压侧地网络连接，最小化该节点上的天线效应，从而减少辐射发射。

- 为抑制电源线的辐射，分别在 VDD 和 GND 线路上串联铁氧体磁珠（图2.2中的FB4、FB5）进行滤波。铁氧体磁珠与去耦电容一起能很好地进行滤波和隔离。在布局区域，铁氧体磁珠需要有效地将芯片布局区域与外围电路分开，避免在不同的PCB层间重叠。磁珠选取在辐射噪声恶劣的频段阻抗较大的型号，能更有效的阻断噪声传播。

- 在长输入信号线的应用场景，可以在差分输入信号线路上串联铁氧体磁珠（图2.2中的FB1、FB2、FB3），以抑制输入信号线上的辐射。

图 2.1 NSI36XX典型应用电路

# 使用集成隔离电源的隔离运放NSI36xx 进行低EMI应用设计

图 2.2 NSI36XX外围电路PCB布局案例

## 3.2.VDD、GND串联磁珠改善EMI

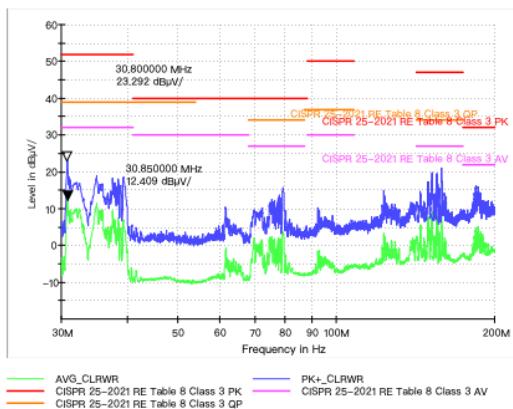

采用2.1节中的PCB布局方案，依据CISPR25标准进行测试，本文中所有的测试结果均在干电池供电、辐射发射较恶劣的水平极化方向测得。

NSI3600D在不增加额外的EMI优化措施条件下的CISPR25辐射发射测试结果如图2.3和图2.4，板上磁珠位置均由0ohm电阻替代。图中可以看到NSI3600D通过CISPR25 CLASS3标准，在30MHz~200MHz频段裕度10dB以上，在200MHz~1GHz频段裕度为2.5dB。

图 2.3 NSI3600D CISPR25 RE测试结果

(30MHz~200MHz, 水平)

图 2.4 NSI3600D CISPR25 RE测试结果

(200MHz~1GHz, 水平)

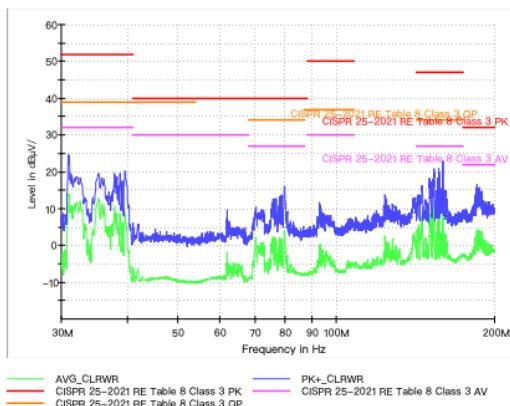

NSI3600D在VDD、GND串联磁珠（BLM18DN601SH1）条件下的CISPR25辐射发射测试结果如图2.5和图2.6，板上输入信号处磁珠位置均由0ohm电阻替代。图中可以看到NSI3600D通过CISPR25 CLASS3标准，在30MHz~200MHz频段裕度为17dB，在200MHz~1GHz频段裕度为5dB。

# 使用集成隔离电源的隔离运放NSI36xx 进行低EMI应用设计

图 2.5 NSI3600D CISPR25 RE测试结果

(30MHz~200MHz, 水平, VDD、GND

串联磁珠BLM18DN601SH1)

图 2.6 NSI3600D CISPR25 RE测试结果

(200MHz~1GHz, 水平, VDD、GND

串联磁珠BLM18DN601SH1)

### 3.3.长输入信号线对EMI的影响

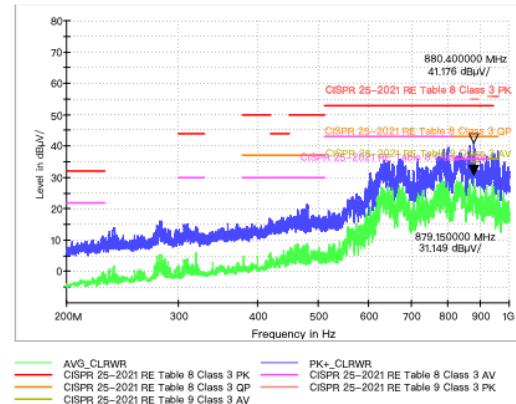

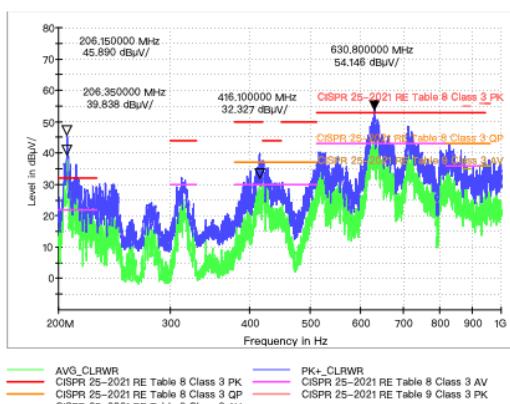

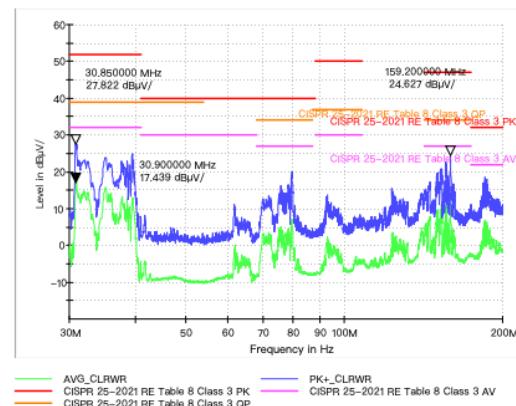

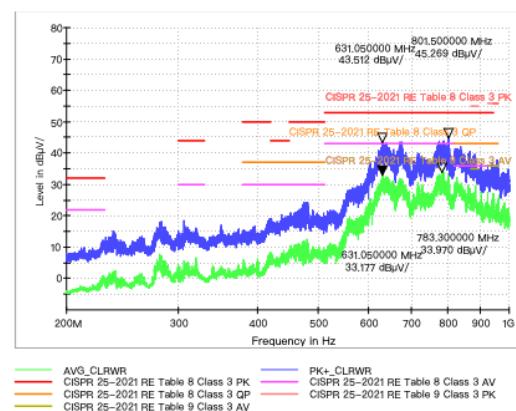

如果NSI3600D的输入信号线较长，长输入信号线会形成天线，恶化芯片的辐射发射。如图2.7所示，在1m长输入信号线条件下，NSI3600D在200MHz~1GHz频段有明显恶化的辐射发射噪声，超过CISPR25 CLASS3标准18dB。

通过在输入信号线上串联磁珠BLM18DN601SH1阻断天线，搭配VDD、GND上串联磁珠BLM18DN601SH1，辐射发射噪声明显被抑制，如图2.8所示，NSI3600D通过CISPR25 CLASS3标准，在30MHz~200MHz频段裕度为9dB。

图 2.7 NSI3600D CISPR25 RE测试结果

(200MHz~1GHz, 水平, 1m长输入信号线)

图 2.8 NSI3600D CISPR25 RE测试结果

(200MHz~1GHz, 水平, VDD、GND和输入信号线

串联磁珠BLM18DN601SH1)

# 使用集成隔离电源的隔离运放NSI36xx 进行低EMI应用设计

## 4.多颗芯片应用中的辐射发射情况

在复杂系统应用或者多路隔离采样应用场景中，通常会有多颗NSI36XX系列产品同时工作的情况，本节给出了多颗NSI3600D同时工作的辐射发射测试结果作为系统设计参考。

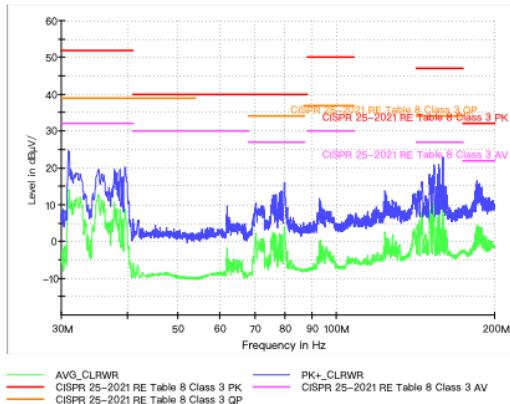

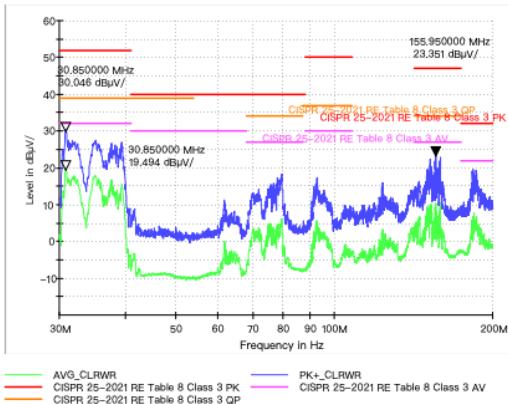

图3.1~图3.3分别给出了1颗、2颗、3颗NSI3600D同时工作时的CISPR25 RE 30MHz~200MHz的测试结果。1颗、2颗、3颗芯片同时工作都通过CISPR25 CLASS3标准，分别对应辐射发射裕度17dB、14.5dB、12.5dB。3颗芯片同时工作相比单颗芯片工作在30MHz~200MHz频段辐射发射恶化了4.5dB。

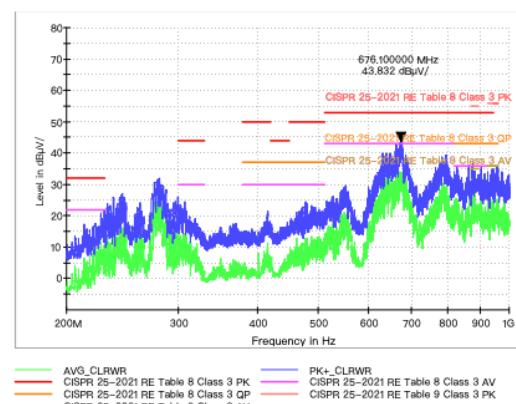

图3.4~图3.6分别给出了1颗、2颗、3颗NSI3600D同时工作时的CISPR25 RE 200MHz~1GHz的测试结果。1颗、2颗、3颗芯片同时工作都通过CISPR25 CLASS3标准，辐射发射裕度均为5dB。3颗芯片同时工作相比单颗芯片工作在200MHz~1GHz频段辐射发射无明显恶化。

综上，多颗NSI36XX系列产品同时工作的应用场景下，辐射发射测试的恶化程度有限。建议客户增加VDD和GND供电线上的串联磁珠，为EMI辐射发射测试留有足够的裕度。

图 3.1 NSI3600D CISPR25 RE测试结果

(30MHz~200MHz, 水平, VDD、GND

串联磁珠BLM18DN601SH1)

图 3.2 2颗NSI3600D CISPR25 RE测试结果

(30MHz~200MHz, 水平, VDD、GND

串联磁珠BLM18DN601SH1)

# 使用集成隔离电源的隔离运放NSI36xx 进行低EMI应用设计

图 3.3 3 颗NSI3600D CISPR25 RE测试结果

(30MHz~200MHz, 水平, VDD、GND

串联磁珠BLM18DN601SH1)

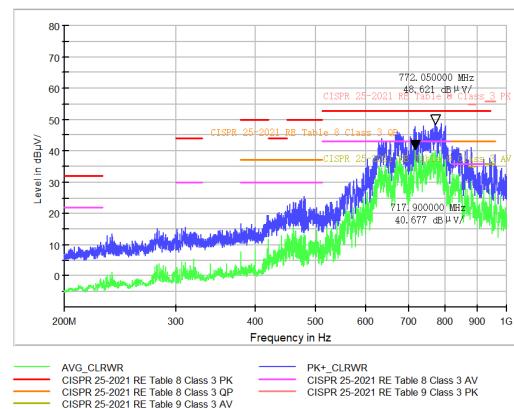

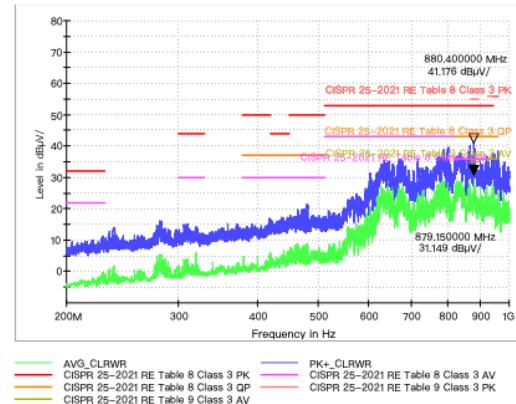

图 3.4 NSI3600D CISPR25 RE测试结果

(200MHz~1GHz, 水平, VDD、GND

串联磁珠BLM18DN601SH1)

图 3.5 2 颗NSI3600D CISPR25 RE测试结果

(200MHz~1GHz, 水平, VDD、GND

串联磁珠BLM18DN601SH1)

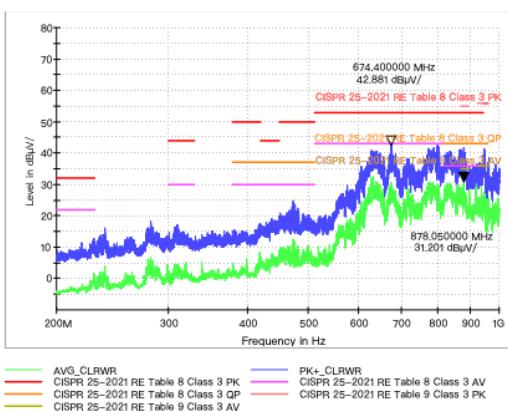

图 3.6 3 颗NSI3600D CISPR25 RE测试结果

(200MHz~1GHz, 水平, VDD、GND

串联磁珠BLM18DN601SH1)

# 使用集成隔离电源的隔离运放NSI36xx 进行低EMI应用设计

## 5.修订历史

| 版本  | 描述     | 作者       | 日期         |

|-----|--------|----------|------------|

| 1.0 | 创建应用笔记 | 徐佳华, 刘雅竹 | 2025/11/28 |

销售联系方式: [sales@novosns.com](mailto:sales@novosns.com); 获取更多信息: [www.novosns.com](http://www.novosns.com)

## 重要声明

本文件中提供的信息不作为任何明示或暗示的担保或授权，包括但不限于对信息准确性、完整性、产品适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的陈述或保证。

客户应对其使用纳芯微的产品和应用自行负责，并确保应用的安全性。客户认可并同意：尽管任何应用的相关信息或支持仍可能由纳芯微提供，但将在产品及其产品应用中遵守纳芯微产品相关的所有法律、法规和相关要求。

本文件中提供的资源仅供经过技术培训的开发人员使用。纳芯微保留对所提供的产品和服务进行更正、修改、增强、改进或其他更改的权利。纳芯微仅授权客户将此资源用于开发所设计的整合了纳芯微产品的相关应用，不视为纳芯微以明示或暗示的方式授予任何知识产权许可。严禁为任何其他用途使用此资源，或对此资源进行未经授权的复制或展示。如因使用此资源而产生任何索赔、损害、成本、损失和债务等，纳芯微对此不承担任何责任。

有关应用、产品、技术的进一步信息，请与纳芯微电子联系（[www.novosns.com](http://www.novosns.com)）。

苏州纳芯微电子股份有限公司版权所有